Driver is available in the precompiled Linux distribution for BBB with installed MPD, basic web interface and other commandline tools. Let's use common environment until all issues will be resolved.

The distribution has integrated support for automatic shutdown of BBB after pressing POWER button. Use it and wait until LEDs are on! If that fails (more than 30 seconds), hold POWER button for 8 seconds. I've already damaged one BBB while removing power cable from the connector while it was on.

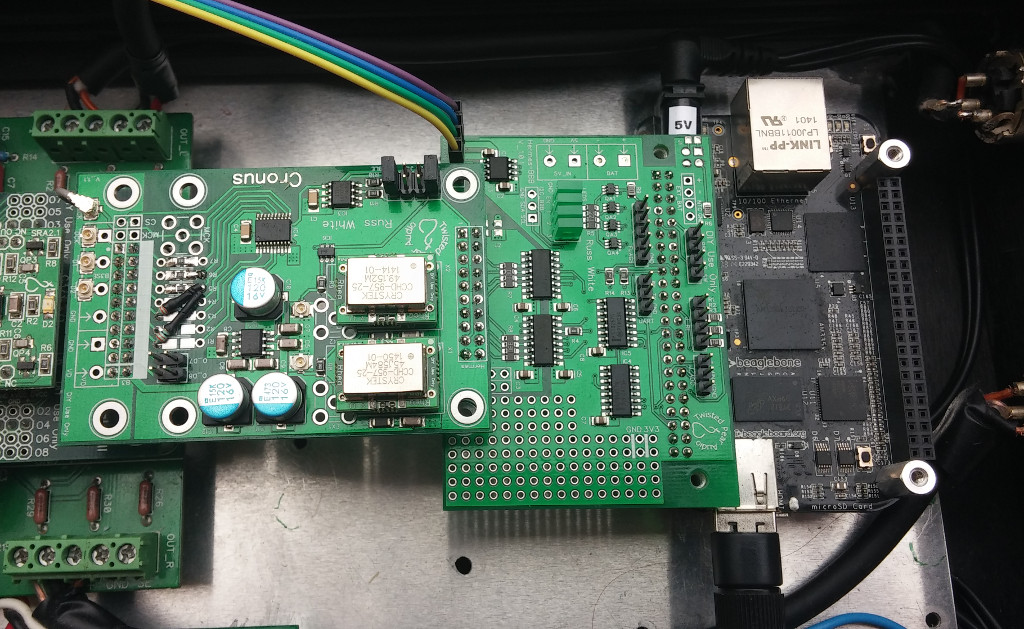

The solution from Twisted Pear Audio is available. It's declared to be open hardware and I've participated in the development process.

Hermes + Cronus + Rhea at Twisted Pear AudioDigital audio chain:

---------------

BBB pin mapping

---------------

P9_25 - A14/0 - mcasp0_ahclkx (oscillator) - GPIO3_21

P9_31 - A13/0 - mcaps0_aclkx (bit clock) - SPI1_SCLK

P9_29 - B13/0 - mcasp0_fsx (lr clock) - SPI1_D0

P9_30 - D12/0 - mcasp0_axr0 (data0) - SPI1_D1

P9_41 - D13/0 - mcasp0_axr1 (data1) - GPIO3_20 shared pin with D14

P9_?? - ?12/2 - mcasp0_axr2 (data2) - configurable, see bellow

P9_27 - C13/2 - mcasp0_axr3 (data3) - GPIO3_19

P9_24 - D15/7 - uart1_txd (external masterclock switch) - GPIO0_15

P9_26 - D16/7 - uart1_rxd (I2S/DSD format switch)- GPIO0_14

P9_14 - U14/7 - gpmc_a2 (cape power switch) - EHRPWM1A

Default mode (kernel param snd_soc_botic.pinconfig=default or not set)

P9_42 - B12/2 - mcasp0_axr2 (data2) - GPIO3_18

Compat mode (kernel param snd_soc_botic.pinconfig=compat)

P9_28 - C12/2 - mcasp0_axr2 (data2) - SPI1_CS0 shared with HDMI audio output

GND is available on any of these pins P9_{01,02,43,44,45,46}.

!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

! Notice:

!!!!!!!!!!!!!

! The current driver shuts down the "cape power switch" right before BBB power down.

! This might not be safe for BBB if cape does not shut down immediatelly too.

! The next driver will have configurable delay between cape shut down and

! BBB shut down.

!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

--------------------

Clocks configuration

--------------------

Installed clocks are configurable via:

- kernel option snd_soc_botic.ext_masterclk

Examples:

0 ... no external clocks, just onboard for 48k freq

1 ... external clock for 44k1 + onboard for 48k

2 ... external clock for 48k only

3 ... external clocks for 44k1 and 48k (default)

+4 ... invert polarity of clock selection switch GPIO0_15

9 ... external clock for 44k1 only

-------------------------------

DSD format switch configuration

-------------------------------

DSD format switch can be configured via:

- kernel option snd_soc_botic.dsd_format_switch

Examples:

0 ... DSD switch is disabled

1 ... DSD switch is enabled (default)

+2 ... invert polarity of format selection switch GPIO0_14

----------------------

Channels configuration

----------------------

Number and offset of channels is configurable via:

- kernel option snd_soc_botic.serconfig

- file /sys/module/snd_soc_botic/parameters/serconfig

which can be updated while system is running, but change

will be applied on the next start of playback

The BBB has 4 serializers and each one is capable to generate:

- one stereo I2S channel

- one mono DSD channel

- one stereo SPDIF channel

Using the "serconfig" option the different serializers can be enabled

and thus allows to change channel number and its offset.

Possible values for each serializer:

M ... I2S/DSD mode

I ... I2S only mode

D ... DSD only mode

S ... SPDIF only mode (exclusive, cannot be combined with I2S/DSD) -- Notice: does not work in botic5

R ... record mode (I2S only)

- ... disabled serializer

Examples:

MMMM ... 8ch I2S output or 4ch DSD output (default)

I--- ... 2ch I2S output on mcasp0_axr0 pin

-I-- ... 2ch I2S output on mcasp0_axr1 pin

--I- ... 2ch I2S output on mcasp0_axr2 pin (old default)

---I ... 2ch I2S output on mcasp0_axr3 pin

DD-- ... 2ch DSD output on mcasp0_axr0 and mcasp0_axr1 pins

MM-- ... 4ch I2S output or 2ch DSD output on mcasp0_axr0 and mcasp0_axr1 pins

--MM ... 4ch I2S output or 2ch DSD output on mcasp0_axr2 and mcasp0_axr3 pins

S--- ... 2ch SPDIF output on mcasp0_axr0 pin

-S-- ... 2ch SPDIF output on mcasp0_axr1 pin

--------

Mute pin

--------

Notice: This parameter is available in botic7

Emulation of mute pin on some of 1-4 data pins:

- kernel option snd_soc_davinci_mcasp.mute_pin

- file /sys/module/snd_soc_davinci_mcasp/parameters/mute_pin

which can be updated while system is running, but change

will be applied on the next start of playback

Supported values for mute_pin:

-1 ... mute pin functionality is disabled

or these additive numbers:

+ 1 ... signal mute on pin 0

+ 2 ... signal mute on pin 1

+ 4 ... signal mute on pin 2

+ 8 ... signal mute on pin 3

+ 16777216 ... invert the mute signal

For example (stereo playback of I2S/DSD on TPA Hermes-BBB):

$ echo 12 > /sys/module/snd_soc_davinci_mcasp/parameters/mute_pin

$ echo MD-- > /sys/module/snd_soc_botic/parameters/serconfig

Two pins are needed, because Hermes-BBB switches pins 2 and 3 when I2S/DSD mode

is switched. After playback start/stop there should appear a mute pin on D5

output pin of Cronus.

----------

DAI format

----------

Clock source and polarity for I2S mode is configurable via:

- kernel option snd_soc_botic.dai_format

- file /sys/module/snd_soc_botic/parameters/dai_format

Supported values:

+1 ... I2S mode

+2 ... Right Justified mode (LSB) -- BUG: does not work in botic4; fixed in botic5

+3 ... Left Justified mode (MSB)

+4 ... L data MSB after FRM LRC

+5 ... L data MSB during FRM LRC

+0 ... NB_NF: normal BCLK & LRCK

+512 ... NB_IF: normal BCLK, inverted LRCK

+768 ... IB_NF: inverted BCLK, normal LRCK

+1024 ... IB_IF: inverted BCLK & LRCK

+4096 ... CBM_CFM: DAC is BCLK & LRCK master

+8192 ... CBS_CFM: DAC is BCLK slave, LRCK master

+12288 ... CBM_CFS: DAC is BCLK master, LRCK slave

+16384 ... CBS_CFS: DAC is BCLK & LRCK slave

Default value: I2S + NB_NF + CBS_CFS

Change via file is active on the next playback start.

--------------------------------

External masterclock frequencies

--------------------------------

External masterclock frequency for 44k1 is configurable via:

- kernel option snd_soc_botic.clk_44k1

- file /sys/module/snd_soc_botic/parameters/clk_44k1

Default value: 22579200

External masterclock frequency for 48k is configurable via:

- kernel option snd_soc_botic.clk_48k

- file /sys/module/snd_soc_botic/parameters/clk_48k

Default value: 24576000

Configured values should be multiple of these frequencies.

Playback is disabled if the value is set to 0.

----------------------

Force BCLK/LRCLK ratio

----------------------

This ratio is configurable via:

- kernel option snd_soc_botic.blr_ratio

- file /sys/module/snd_soc_botic/parameters/blr_ratio

For I2S mode default value is 64.

Other valid values are 32 and 48 (and maybe others).

Linux kernel with integrated Botic driver (select a branch and check the patches/botic directory)